## 产品特性

- 双路输出可调电压

- 可控制上电顺序

- 调整器 1 输出电流可达 1A,调整器 2 输出电流可达 2A

- 快速瞬态响应

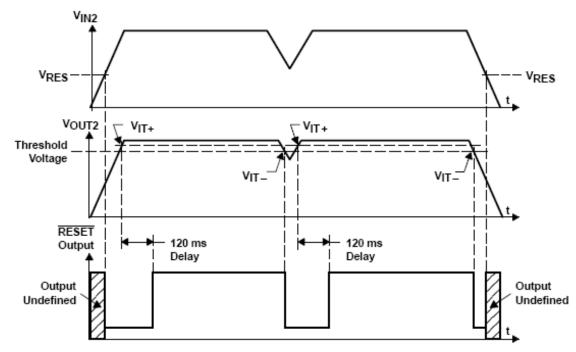

- 复位端开漏输出,上电复位延迟 120ms(典型值)

- 调整器 1 输出状态指示 Power Good 端开漏输出

- 超低静态电流,255µA(典型值)

- 低待机电流: 10µA (典型值)

- 输出电容快速放电

- 双复位

- 欠压锁存特性(UVLO)

- 过热保护

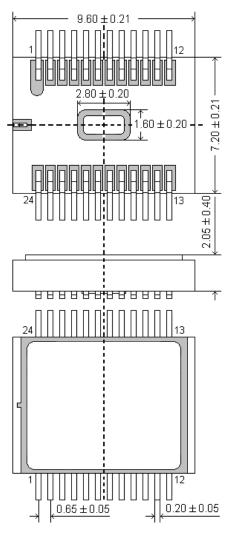

- 24线带热沉陶瓷扁平封装

- 抗总剂量 100krad (Si)

## 产品概述

LPS70302型双路输出低压差线性 稳压器可提供超低漏失电压及带有上 电顺序控制的双路输出电压,其主要 应用于 DSP、FPGA、ASIC 和大规模 数字集成电路等系统。电路具有低噪 声特点,不需任何旁路电容,并且具 有快速瞬态响应特点,为用户提供了 完整的电源解决方案。

调整器 1 输出电流可达 1A,调整器 2 输出电流可达 2A。两路调整器具有分离的输入电压端,可使用户根据需要配置。

功率管采用具有低导通电阻特性的 PMOS 器件,电路漏失电压很小(调

整器 1 典型值 160mV)且与输出电流 成正比; PMOS 功率管采用电压调整 方式,电路整体静态功耗很小且与输 出负载大小无关(全负载范围内静态 功耗最大 250μA)。电路具有待机模 式,当使能端为高时两路输出均关闭, 电源电流可低至 10μA。

使能端输出为低时电路启动,两调整器的输出电压分别通过 V<sub>FB1</sub> 和 V<sub>FB2</sub>端口进行监测。SEQ 端控制 L<sub>DO1</sub> 和 L<sub>DO2</sub>的上电顺序,当器件使能并且 SEQ 被拉到高电位或悬空时 V<sub>OUT2</sub> 首先打开,V<sub>OUT1</sub> 仍关断,直到 V<sub>OUT2</sub> 到达其输出电压的 83%时 V<sub>OUT1</sub> 打开。在某些情况(如:过负载状态)下若 V<sub>OUT2</sub> 被拉至其 83%以下时,V<sub>OUT1</sub> 被关断。当 SEQ 为低时,上电顺序会改变,此时 V<sub>OUT1</sub> 会先开启。SEQ 端内部连接一上拉电流源,当其悬空时,SEQ 端相当于被置为高电平。

每个调整器内部均有放电结构, 当电路被关断时,通过放电结构可快 速放掉输出电容上的多余电荷。

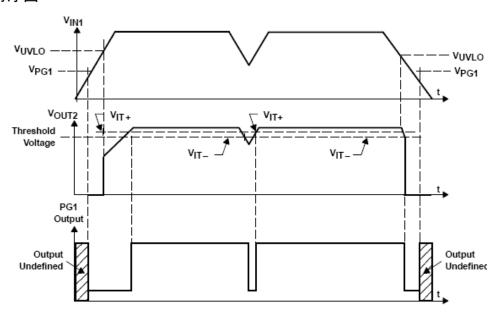

PG1 端指示调整器 1 的工作状态,可作为与调整器 1 输出相连电路的上电复位端。

RESET 端为开漏输出,低电平有效。正常工作时需接上拉电阻,当上拉时,RESET 端口在满足以下全部 3 个条件时经约 120ms 延迟后进入高阻态:①V<sub>INI</sub> 必须在欠压锁存电压条件以上;②手动复位 MRI、MR2 必须为高阻态;③V<sub>OUT2</sub> 必须在其调节输出电压的 95%以上。为监测 V<sub>OUT1</sub>,PG1 端口可被连接至 MRI 或 MR2。 RESET 端口

RESET端在不使用时可被悬空。

内部基准电压由 $V_{INI}$ 驱动。当 $V_{INI}$  在输入电压大于 2.5V 时开启。

可用作上电复位端或低电指示端, 大于 2.8V 后, 电路正常工作。每路调 节器均具有欠压锁存功能, 保证电路

# 绝对最大额定参数

| $V_{\rm IN1}$ 、 $V_{\rm IN2}$ 输入电压范围          | $-0.3 \text{ V}{\sim}5.5\text{V}$ |

|-----------------------------------------------|-----------------------------------|

| EN 端口电压范围                                     | −0.3 V~5.5V                       |

| RESET, PG1 端最大电压                              | 7.0V                              |

| 最大输出电压(V <sub>OUT1</sub> 、V <sub>OUT2</sub> ) | 4.3V                              |

| MRI、MR2和 SEQ 端最大电压                            | $ m V_{IN1}$                      |

| 结温(TJ)                                        | 150°C                             |

| 储存温度范围(Tstg)                                  | -65°C∼150°C                       |

| 最大功耗 (P <sup>D</sup> )                        | 1.0 W(常温)                         |

| 引线耐焊接温度(Th)(10s)                              | 300℃                              |

| 静电放电敏感度 (ESDS)                                | 1000V                             |

## 推荐工作条件

| V <sub>IN1</sub> 输入电压范围  | $2.8V \sim 5.0V$                |

|--------------------------|---------------------------------|

| V <sub>IN2</sub> 输入电压范围  | $2.8V \sim 5.0V$                |

| V <sub>OUT1</sub> 输出电压范围 | $V_{REF}\sim4.0V$               |

| V <sub>OUT2</sub> 输出电压范围 | $V_{REF}\sim4.0V$               |

| LDO1 输出电流                | $1 \text{mA} \sim 1.0 \text{A}$ |

| LDO2 输出电流                | $1 \text{mA} \sim 2.0 \text{A}$ |

| 环境温度(TA)                 | -55°C ∼ 125°C                   |

# 电参数表

若无其它规定,测试条件如下:工作温度: -55℃~+125℃; V<sub>INI</sub>=4.3V,  $V_{OUT1}$ =3.3V、 $V_{IN2}$ =2.8V,  $V_{OUT2}$ 与 $V_{FB2}$ 短接, $I_{OUT1}$ =1mA, $I_{OUT2}$ =1mA, $\overline{\it EN}$ =0V,  $C_{OUT1}{\geqslant}22\mu F\text{, }C_{OUT2}{\geqslant}47\mu F\text{.}$

| 参数名称              |                          | 测试条件                                                      | 极限值   |       | 单位   |

|-------------------|--------------------------|-----------------------------------------------------------|-------|-------|------|

|                   |                          | 例以家厅                                                      | 最小值   | 最大值   | 4.07 |

| V <sub>O</sub> 输出 | 输出电压(V <sub>OUT1</sub> ) | 2.8V≤V <sub>IN1</sub> ≤5.0V<br>V <sub>OUT1</sub> 与 FB1 短接 | 1.196 | 1.248 | V    |

| 电压 <sup>(a)</sup> | 输出电压(V <sub>OUT1</sub> ) | V <sub>INI</sub> =5.0V<br>使 V <sub>OUTI</sub> =4.0V       | 3.920 | 4.080 | V    |

| 参数名称                                                        |                          | 油小+ 友 44-                                                                                                                                                                         | 极限值   |          | 苗台              |

|-------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|-----------------|

|                                                             |                          | 测试条件                                                                                                                                                                              | 最小值   | 最大值      | 单位              |

| Vo 输出                                                       | 输出电压(V <sub>OUT2</sub> ) | 2.8V≤V <sub>IN2</sub> ≤5.0V<br>V <sub>OUT2</sub> 与 FB2 短接                                                                                                                         | 1.196 | 1.248    | - V             |

| 电压 <sup>(a)</sup>                                           |                          | V <sub>IN2</sub> =5.0V<br>使 V <sub>OUT2</sub> =4.0V                                                                                                                               | 3.920 | 4.080    |                 |

| 静态电流(调 <sup>-</sup><br>EN=0V <sup>(a)</sup>                 | 节器1和2的地电流),              | 见 <sup>(b)</sup>                                                                                                                                                                  | _     | 250      | μА              |

| 输出电压线性<br>见 <sup>(c)</sup>                                  | 调整率(调节器1和2)              | 2.8V≤V <sub>INI</sub> ≤5.0V<br>V <sub>OUT1</sub> 与 FB1 短接<br>2.8V≤V <sub>IN2</sub> ≤5.0V<br>V <sub>OUT2</sub> 与 FB2 短接                                                            | _     | 0.5      | %/V             |

| V <sub>OUT1</sub> 和 V <sub>OUT2</sub> 的负载调整率 <sup>(b)</sup> |                          | $2.8V \leqslant V_{INI} \leqslant 5.0V$ $V_{OUTI} = FB1$ 短接 $2.8V \leqslant V_{IN2} \leqslant 5.0V$ $V_{OUT2} = FB2$ 短接 $V_{IN1} = V_{IN2} = 5.0V$ 使 $V_{OUT1} = V_{OUT2} = 4.0V$ | _     | 30       | mV              |

| I <sub>I</sub> 待机电流                                         |                          | $\overline{\it EN}$ =V $_{ m IN}$                                                                                                                                                 | _     | 10       | μΑ              |

| 1113-70 11-11010                                            |                          | LIV VIN                                                                                                                                                                           | _     | 20       | μ2 1            |

| RESET 端口                                                    |                          |                                                                                                                                                                                   |       | <b>.</b> |                 |

| 有效 <b>RESET</b> 的                                           | 员最小输入电压                  | $I_{(\overline{RESET})} = 300 \mu A,$ $V_{(\overline{RESET})} \leq 0.8 V$                                                                                                         | _     | 1.6      | V               |

| Trip 阈值电压                                                   |                          | 降低 V <sub>O</sub>                                                                                                                                                                 | 85    | 98       | %V <sub>O</sub> |

| $t_{(\overline{RESET})}$                                    |                          | RESET 脉冲持续时间                                                                                                                                                                      | 80    | 160      | Ms              |

| 输出低电压                                                       |                          | $V_{IN}=3.5V, I_{(\overline{RESET})}=1mA$                                                                                                                                         | _     | 0.6      | V               |

| 漏电流                                                         |                          | $V_{(\overline{RESET})}=6V$                                                                                                                                                       | _     | 1.0      | μΑ              |

| PG1 端口                                                      |                          |                                                                                                                                                                                   | •     | •        |                 |

| 有效 PG1 的最                                                   | <b></b>                  | $I_{(PG1)}=300\mu A,$ $V_{(PG1)} \leq 0.8V$                                                                                                                                       | _     | 1.6      | V               |

| Trip 阈值电压                                                   |                          | 降低 Vo                                                                                                                                                                             | 85    | 98       | %V <sub>O</sub> |

| 输出低电压                                                       |                          | $V_{IN}=2.8V, I_{(PG1)}=1mA$                                                                                                                                                      | _     | 0.6      | V               |

| 漏电流                                                         |                          | V <sub>(PG1)</sub> =6V                                                                                                                                                            | _     | 1.0      | μΑ              |

| EN端口                                                        |                          |                                                                                                                                                                                   |       |          |                 |

| EN输入高电平 <sup>(d)</sup>                                      |                          |                                                                                                                                                                                   | 2.4   | _        | V               |

| EN输入低电平 <sup>(d)</sup>                                      |                          |                                                                                                                                                                                   | _     | 0.6      | V               |

| 输入电流(EN)                                                    |                          |                                                                                                                                                                                   | -5    | 5        | μΑ              |

| SEQ 端口                                                      |                          |                                                                                                                                                                                   |       |          |                 |

| SEQ 输入高电平 <sup>(d)</sup>                                    |                          |                                                                                                                                                                                   | 2.4   | _        | V               |

| SEQ 输入低电平 <sup>(d)</sup>                                    |                          |                                                                                                                                                                                   | _     | 0.6      | V               |

| MR1/MR2 端                                                   |                          |                                                                                                                                                                                   |       |          |                 |

| 输入高电平 <sup>(d)</sup>                                        |                          |                                                                                                                                                                                   | 2.4   | _        | V               |

| 参数名称                                                                        | 测试条件                                      | 极限值 |     | 出台                 |  |

|-----------------------------------------------------------------------------|-------------------------------------------|-----|-----|--------------------|--|

| 多                                                                           |                                           | 最小值 | 最大值 | 单位                 |  |

| 输入低电平 <sup>(d)</sup>                                                        |                                           | _   | 0.6 | V                  |  |

| V <sub>OUT2</sub> 端口                                                        |                                           |     |     |                    |  |

| V <sub>OUT2</sub> 欠压 (UV) 比较器: 在 V <sub>OUT1</sub> 欠压 (UV) 比较器的正向输入阈值<br>电压 |                                           | 70  | 95  | $% V_{\mathrm{O}}$ |  |

| V <sub>OUT1</sub> 端口                                                        |                                           |     |     |                    |  |

| V <sub>OUT1</sub> 欠压 (UV) 比较器: 在 V <sub>OUT2</sub> 欠压 (UV) 比较器的正向输入阈值<br>电压 |                                           | 70  | 95  | $% V_{\mathrm{O}}$ |  |

| 漏失电压 <sup>(e)</sup>                                                         | I <sub>O</sub> =1A,V <sub>IN1</sub> =3.2V | _   | 255 | mV                 |  |

| V <sub>IN1</sub> /V <sub>IN2</sub> 端口                                       |                                           |     |     |                    |  |

| UVLO 阈值                                                                     |                                           | 2.0 | 3.0 | V                  |  |

| FB1∖FB2 端口                                                                  |                                           |     |     |                    |  |

| FB1\FB2 输入电流                                                                | FB1\FB2=1.8V                              | _   | 2   | μΑ                 |  |

- (a) 最小输入电压 V<sub>INI</sub>=V<sub>IN2</sub>=2.8V, 最大输入电压=5.0V;

- $^{(b)}$  对调节器 1,  $I_{O}$ =1mA~1.0A; 对调节器 2,  $I_{O}$ =1mA~2.0A;

- (c) 对于 V<sub>OUT1</sub>/V<sub>OUT2</sub> 输出:

$V_{OUTX}$   $\leq$  1.8V 时,线性调整率(mV)=(%/V)× $V_{OUTX}$   $\frac{(5.0-2.8)}{100}$  × 1000

$V_{OUTX}>1.8V$  时,线性调整率(mV)=(%/V) $\times V_{OUTX}$  $\frac{(5.0-V_{OUTX}-1)}{100} \times 1000;$

- (d) 若本参数作为强制测试条件已应用在其它参数测试过程中,则本参数可不必测。

- $^{(e)}$  将  $V_{INI}$  输入电压设置为 3.2V, $V_{OUTI}$  输出电压设置为 3.3V 时测试。

# 典型工作特性

$\overline{RESET}$  时序图(当 VIN1 开始启动, $\overline{MR1}$  和  $\overline{MR2}$  处于高电平)

## PG1 时序图

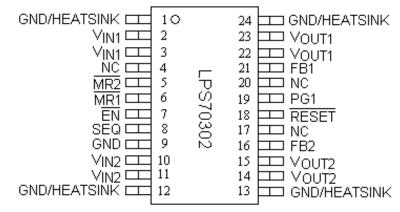

# 引脚描述

| 序<br>号 | 符号               | 功能        | 序<br>号 | 符号             | 功能                         |

|--------|------------------|-----------|--------|----------------|----------------------------|

| 1      | GND/HEATSINK     | 地/热沉      | 13     | GND/HEATSINK   | 地/热沉                       |

| 2      | $ m V_{IN1}$     | LDO1 输入电源 | 14     | $ m V_{OUT2}$  | LDO2 输出端                   |

| 3      | $V_{\rm IN1}$    | LDO1 输入电源 | 15     | $V_{\rm OUT2}$ | LDO2 输出端                   |

| 4      | NC               | 空         | 16     | FB2            | LDO2 反馈端                   |

| 5      | MR2              | 手动复位 2    | 17     | NC             | 空                          |

| 6      | $\overline{MR1}$ | 手动复位 1    | 18     | RESET          | 复位端                        |

| 7      | $\overline{EN}$  | 使能端       | 19     | PG1            | V <sub>OUT1</sub><br>输出指示端 |

| 8      | SEQ              | 上电顺序控制端   | 20     | NC             | 空                          |

| 9      | GND              | 地         | 21     | FB1            | LDO1 反馈端                   |

| 10     | $V_{\rm IN2}$    | LDO2 输入电源 | 22     | $V_{OUT1}$     | LDO1 输出端                   |

| 11     | $V_{IN2}$        | LDO2 输入电源 | 23     | $V_{OUT1}$     | LDO1 输出端                   |

| 12     | GND/HEATSINK     | 地/热沉      | 24     | GND/HEATSINK   | 地/热沉                       |

## 引脚功能

## 使能 (EN)

使能端能够启动或关断电路,当使能为高电平时,电路关断。当使能跳转为 低电平时,电路启动。

## 上电顺序控制 (SEO)

SEQ 端用来控制两路输出的上电顺序。当 SEQ 为高电平或悬空时, $V_{OUT2}$  先启动,此时  $V_{OUT1}$  保持关断。当  $V_{OUT2}$  电压达到正常值的 83%时, $V_{OUT1}$  启动。若出现  $V_{OUT2}$  被拉低到 83%以下时(例如:过载状态), $V_{OUT1}$  将被关断。该端口由  $V_{IN1}$  提供一个 6uA 的上拉电流。

当 SEQ 为低电平时,上电顺序改变,此时 VOUTI 先启动。

## 电压正常 (PG1)

该端口为开漏极高有效输出端口,指示第一路输出电压的状态。当  $V_{OUT1}$  达到正常电压的 95%时,PG1 跳转为高阻态。当  $V_{OUT1}$  被拉低到 95%以下时,PG1 跳转为低阻态。PG1 引脚的开漏极输出需要一个上拉电阻。

### 手动复位( $\overline{MR1}$ , $\overline{MR2}$ )

$\overline{MR1}$ 和 $\overline{MR2}$ 端为复位触发信号输入端,低电平有效。当是 $\overline{MR1}$ 或 $\overline{MR2}$ 被拉至低电平时,复位功能启动。该端口由  $V_{INI}$ 提供  $6\mu A$  上拉电流。若这些引脚不用时,推荐将其与  $V_{IN}$  连接。

#### 反馈(FB1, FB2)

FB1 和 FB2 是可调输出电路的反馈输入端,与外部分压电阻连接。FB1/FB2 与分压电阻的连接线应当尽可能短,这样能够减小或消除噪声采集。不建议在FB 端到 V<sub>OUT</sub> 端之间添加 RC 滤波网络,因为这样能够导致输出电压震荡。

#### 复位指示 (RESET)

$\overline{RESET}$  端为开漏极输出,通过上拉电阻工作,低电平有效。当电路工作,满足以下三个条件时, $\overline{RESET}$  端将经过 120ms 延迟后变为高阻态(高电平)。第一, $V_{IN1}$  电压大于最小工作电压;第二,手动复位端 $\overline{MR}$  为高阻态;第三, $V_{OUT2}$  电压大于正常输出电压的 95%。为了监测  $V_{OUT1}$ , $\overline{MR1}$ 或  $\overline{MR2}$  可以与 PG1 端相连。

#### VINI和 VIN2

$V_{IN1}$  和  $V_{IN2}$  是调整器的输入引脚。

#### Vouti和 Vouti

Vourt 和 Vourz 是调整器的输出引脚。

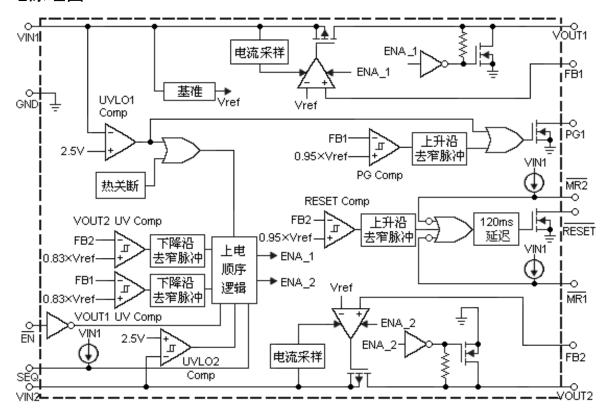

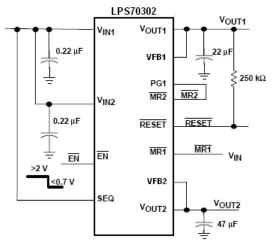

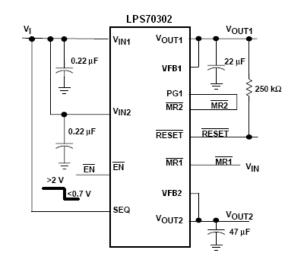

## 电原理图

注释: A. 对于大多数应用,器件的  $V_{FB1}$  和  $V_{FB2}$  应该在外部尽可能近地连接到其相应的  $V_{OUT}$  输出。

B. 如果 SEQ 引脚在输入中悬空, V<sub>OUT2</sub> 先启动。

## 功能描述

LPS70302 型双路输出可调低压差线性稳压器能够为 DSP 应用提供高性能、且具有双路上电顺序控制的电源管理解决方案。该电路具有高精度和快速瞬态响应的特点,并且具备低静态电流的特性。上电顺序可控的电源解决方案使得 DSP 应用中不需要其他外部控制器件。在减少元器件成本和电路板面积的同时能够提高系统的整体可靠性。LPS70302 型低压差线性稳压器具有使能功能,它能够使电路进入睡眠模式,此时输入电流较小,可低至 10uA。另外,还集成了 SVS(上电复位,低电平有效)和输出电压状态指示功能。这些功能能够检测输出电压并为系统提供一个逻辑电平信号。总之,LPS70302 为 DSP 应用提供一个完整的电源解决方案。

LPS70302 具有极低的静态电流,并且在不同负载下,其静态电流几乎不变。 LPS70302 采用 PMOS 管作为调整管,由于 PMOS 管栅极由电压驱动,因此在满载工作时仍然能够保持很小并且稳定的静态电流。

## 应用手册

### 地/热沉

在系统允许的情况下,设计时应尽可能大的增加板级热沉的面积,且器件的 热沉与板级热沉之间应采用焊接方式进行良好接触,以提高系统的散热性能。

## 输入电容

在典型应用中,为确保器件稳定,输入端推荐添加一个陶瓷旁路电容 (0.22μF-1μF)。此电容应离输入引脚尽可能的近。由于输入阻抗的影响,大输入瞬态电流会引起输入电压下降。如果电压下降到引起输入电压低于 UVLO 阈值电压,器件会关断。因此,推荐使用大电容与瓷片旁路电容平行放置在调整器的输入端。此电容的大小取决于输出电流、主电源响应时间、主电源到调整器的距离。电容器的大小至少应确保输入电压在正常运行下不低于 UVLO 阈值电压。

#### 输出电容

像大多数 LDO 调整器一样,LPS70302 每一路需要在输出和地之间连接输出电容,确保内部控制环路稳定。对于  $V_{OUT1}$  推荐的最小值是 22uF 并且 ESR(等效串联电阻)必须在  $50m\Omega$  到  $800m\Omega$ 。对于  $V_{OUT2}$  推荐的最小值是 47uF 并且 ESR(等效串联电阻)必须在  $50m\Omega$  到  $2\Omega$ 。固体钽电容、铝电解电容、多层陶瓷电容在满足上述需求的情况下均可以使用。更大容值的电容可提供更大范围的稳定和更好的负载瞬态响应。

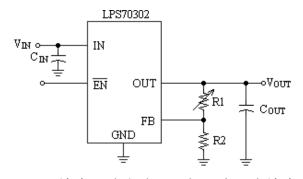

#### LPS70302 输出可调的 LD0 稳压器

LPS70302 可调输出网路电路图(仅示意一个输出端口)

可调输出的反馈网路通过设置 R2、R1 的阻值可改变电阻网络的分流、通常这一分流约为  $40\mu A$ ,推荐选取 R2= $30.1k\Omega$ ,R1=[( $V_{OUT}/V_{REF}$ )-1]×R2,其中  $V_{REF}$ =1.214V。

| 市川棚山屯江町屯田門山及川直 |      |      |    |  |

|----------------|------|------|----|--|

| 输出电压           | R1   | R2   | 单位 |  |

| 1.8V           | 14.5 | 30.1 | kΩ |  |

| 2.5V           | 31.9 | 30.1 | kΩ |  |

| 3.3V           | 51.7 | 30.1 | kΩ |  |

常用输出电压的电阻网络设计值

可选用低阻值的电阻,但对提高输出电压精度作用不大,并且会浪费更多的电源电流;通常不建议采用高阻值的电阻,因为在 FB 端的漏电流的作用下,实际输入到 FB 端电压的值与设计的电阻网络输出值会有一定误差,对输出电压的精度产生影响。

选用温度系数相同或相近的电阻组成电阻网络,以避免在高低温环境下由于电阻温度系数不同引起输出电压与设计值不符。

应用时反馈电阻网络间互联线要尽可能的短,并且尽量靠近器件,减小板级寄生电阻对输出电压的影响,同时避免噪声从  $V_{FB1}$  和  $V_{FB2}$  端口进入器件系统中;禁止在  $V_{FB1}$  和  $V_{OUT1}$  或  $V_{FB2}$  和  $V_{OUT2}$  之间增加 RC 网络来滤波,因为这可能引起系统的振荡。

### 稳压器保护

LPS70302 的两路 PMOS 功率管都内置了控制反向电流的二极管,当输入压差低于输出电压(例如:关断期间),使电流由输出到输入传输不受内部限制。 当有长时间的反向模式发生时,需要对此增加外部限制。

LPS70302 具有内部限流和热保护功能。在正常运行期间,LPS70302 的调整器 1 输出电流限制在大约 1.75A(典型),调整器 2 输出电流限制在大约 3.8A(典型)。当在限流模式下,输出电压线性减小直到过流状态结束。而限流的目的是防止器件损坏,在使用时器件总功耗不应超过封装可承受的功耗。如果器件的温度超过 150℃(典型),热保护电路将关断器件。一旦器件温度降到 130℃(典型)以下,稳压器继续开始运行。

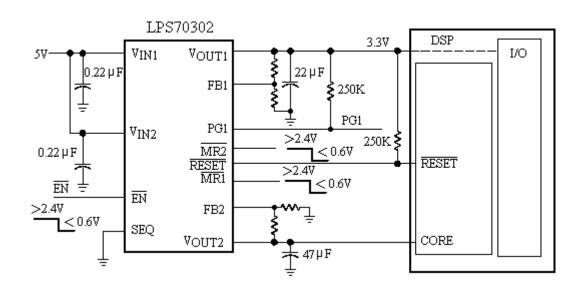

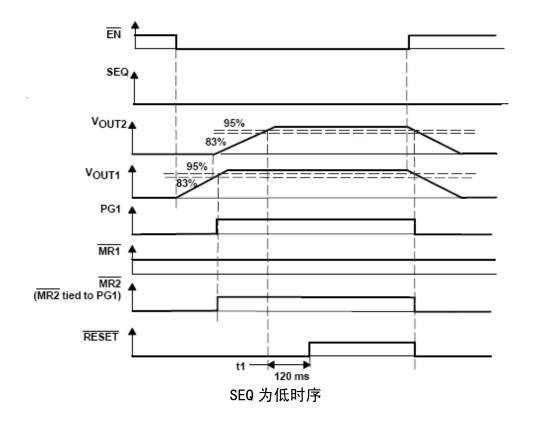

## 典型应用

## 下列情况未标注在应用示意图中:

$V_{IN1}$  和  $V_{IN2}$  设置为相同的固定输入电压,且都大于  $V_{UVLO}$ ; SEQ 设置为逻辑低电平; PG1 与  $\overline{MR2}$  连接; 未使用  $\overline{MR1}$ ,  $\overline{MR1}$  与  $V_{IN}$  短接。

## 时序图的说明:

$\overline{EN}$  初始为高; 此时两路输出都关断,并且 PG1 和  $\overline{RESET}$  处于低电平。当  $\overline{EN}$  变为低电平时,SEQ 为低电平。  $V_{OUT1}$  先启动。在  $V_{OUT1}$  达到正常输出电压的 83%后  $V_{OUT2}$  打开。当  $V_{OUT1}$  达到正常输出电压的 95%时,PG1(接到  $\overline{MR2}$ )跳转为高电平。当  $V_{OUT1}$  和  $V_{OUT2}$  分别达到正常输出电压的 95%,且  $\overline{MR1}$  和  $\overline{MR2}$  (接到 PG1)都处于高

电平时;经过 120ms 延时后, $\overline{RESET}$ 被拉到高电平。当 $\overline{EN}$ 变为高电平时,电路关断,且  $\overline{PG1}$ (接到 $\overline{MR2}$ )和 $\overline{RESET}$ 都变为低电平。

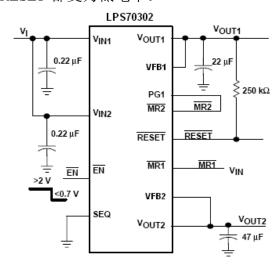

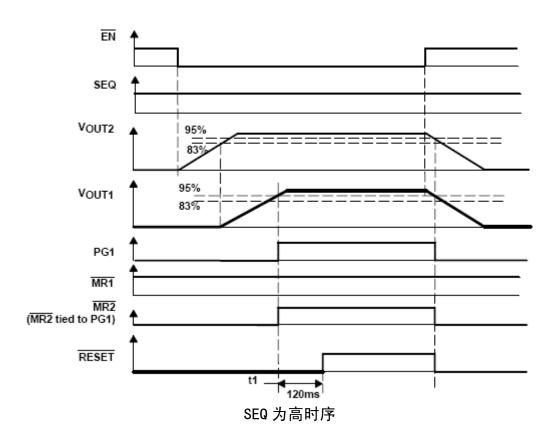

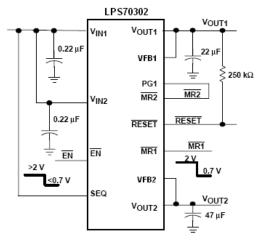

## 下列情况未标注在应用示意图中:

$V_{IN1}$  和  $V_{IN2}$  设置为相同的固定输入电压,且都大于  $V_{UVLO}$ ; SEQ 设置为逻辑低电平; PG1 设置为 $\overline{MR2}$ ; 未使用 $\overline{MR1}$ ,  $\overline{MR1}$ 与  $V_{IN}$ 短接。

## 时序图的说明:

$\overline{EN}$  初始为高; 此时两路输出都关断,并且 PG1 和  $\overline{RESET}$  处于低电平。当  $\overline{EN}$  变为低电平时,SEQ 为高电平。  $V_{OUT2}$  先启动。在  $V_{OUT2}$  达到正常输出电压的 83%后  $V_{OUT1}$  打开。当  $V_{OUT1}$  达到正常输出电压的 95%时,PG1(接到  $\overline{MR2}$ )跳转为高电平。当  $V_{OUT1}$  和  $V_{OUT2}$  分别达到正常输出电压的 95%,

且 $\overline{MR1}$ 和 $\overline{MR2}$  (接到PG1)都处于高电平时;经过120ms延时后, $\overline{RESET}$ 被拉到高电平。当 $\overline{EN}$ 变为高电平时,电路关断,且PG1(接到 $\overline{MR2}$ 和 $\overline{RESET}$ 都变为低电平。

## 下列情况未标注在应用示意图中:

$V_{IN1}$  和  $V_{IN2}$  设置为相同的固定输入电压,都大于  $V_{UVLO}$ ; SEQ 设置为高电平; PG1 接  $\overline{MR2}$ ; 初始  $\overline{MR1}$  为高电平,经过一段时间后切换为低电平。

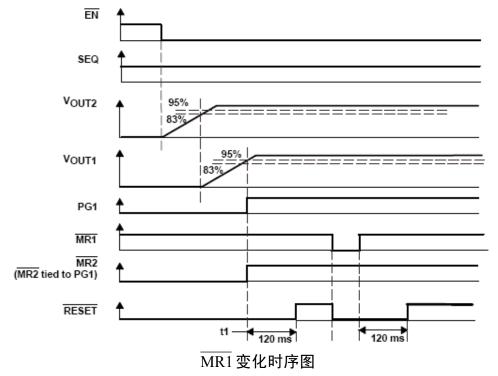

## 时序图的说明:

$\overline{EN}$  初始为高;此时两路都关断,并且 PG1 和  $\overline{RESET}$  处于低电平。当  $\overline{EN}$  为低电平时,SEQ 处于高电平。 $V_{OUT2}$  先启动。在  $V_{OUT2}$  达到正常出电压的 83%后  $V_{OUT1}$  打开。当  $V_{OUT1}$  达到正常输出电压的 95%时,PG1(接到  $\overline{MR2}$ )变为高电平。当  $V_{OUT1}$  和  $V_{OUT2}$  分别达到正常输出电压的 95%,且  $\overline{MR1}$  和  $\overline{MR2}$  (接到 PG1)都处于高电平时;经过 120ms 延时, $\overline{RESET}$  被

拉到逻辑高电平。当 $\overline{MRI}$ 变为低电平时, $\overline{RESET}$ 变为低电平,但是输出电压不变。当 $\overline{MRI}$ 变回逻辑高电平时,因为 $V_{OUT1}$ 和 $V_{OUT2}$ 都保持在各自正常输出电压的 95%以上,并且 $\overline{MR2}$ (接 $\overline{PG1}$ )为高电平,经过 120ms延时, $\overline{RESET}$ 变为高电平。

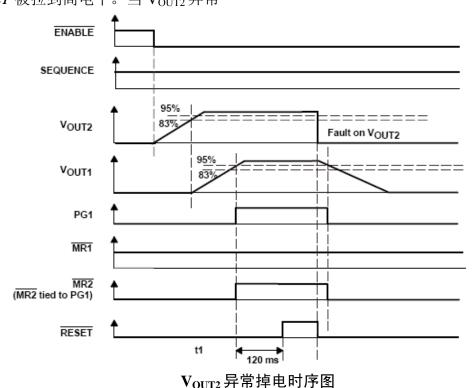

### 下列情况未标注在应用示意图中:

$V_{IN1}$  和  $V_{IN2}$  设置为相同的固定输入电压,且都大于  $V_{UVLO}$ ; SEQ 设置为高电平; PG1 接  $\overline{MR2}$ ; 未使用  $\overline{MR1}$ ,  $\overline{MR1}$ 与  $V_{IN}$  短接。

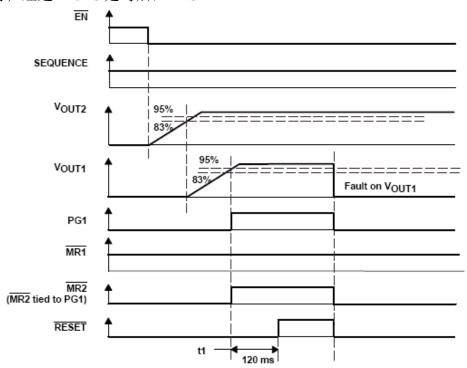

## 时序图的说明:

$\overline{EN}$  初始为高; 此时两路输出都关断,并且 PG1 和 $\overline{RESET}$  处于低电平。当 $\overline{EN}$  为低电平时,SEQ 处于高电平。  $V_{OUT2}$  先启动。在  $V_{OUT2}$  达到正常输出电压的 83%后  $V_{OUT1}$  打开。当  $V_{OUT1}$  达到正常输出电压的 95%时,PG1(接到 $\overline{MR2}$ )跳转到高电平。当  $V_{OUT1}$  和  $V_{OUT2}$  分别达到正常输出电压的 95%,并且  $\overline{MR1}$  和  $\overline{MR2}$  接到 PG1)都处于高电平时;经过 120ms 延时后, $\overline{RESET}$

被拉到高电平。当 $V_{OUT1}$ 不正常掉电时,导致输出电压下降到正常输出电压的 95%以下,PG1(接 $\overline{MR2}$ )跳转到低电平。

Vourt 异常掉电时序图

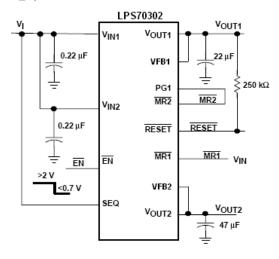

### 下列情况未标注在应用示意图中:

$V_{IN1}$  和  $V_{IN2}$  设置为相同的固定输入电压,都大于  $V_{UVLO}$ ; SEQ 设置为高电平; PG1 接 $\overline{MR2}$ ; 未使用 $\overline{MR1}$ ,  $\overline{MR1}$ 与  $V_{IN}$ 短接

## 时序图的说明:

EN 初始为高;此时两路输出都关断,并且 PG1 和 RESET 处于低电平。当 EN 为低电平时,SEQ 处于逻辑高电平。Vout2 先启动。在 Vout2 达到正常输出电压的 83%后 Vout1 打开。当Vout1 达到正常输出电压的 95%时,PG1(接到 MR2)跳转到高电平。当Vout1 和 Vout2 分别达到正常输出电压的 95%,并且 MR1 和 MR2(接到 PG1)都处于高电平时;经过 120ms 延时后,RESET 被拉到高电平。当 Vout2 异常

掉电时,输出电压下降到正常输出电压的 95%以下, $\overline{RESET}$  变回低电平,且因为 SEQ 是高电平,则  $V_{OUT1}$  开始关断。当  $V_{OUT1}$  下降到正常输出电压的 95%以下,PG1(接 $\overline{MR2}$ )跳转到低电平。

# 封装信息

器件采用带热沉的 CSOP24K 型陶瓷小外形外壳封装。单位: mm